ADC is an irresistible topic for a Nyquist ADC designer. Several years ago I touched a bit of it when I studied noise-shaping SAR ADC. Recently I have the opportunity to revisit this topic.

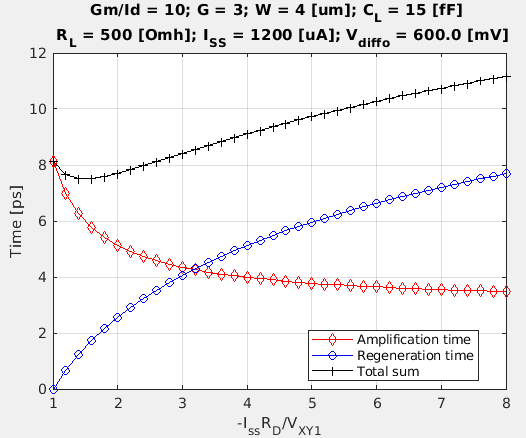

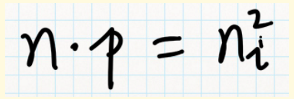

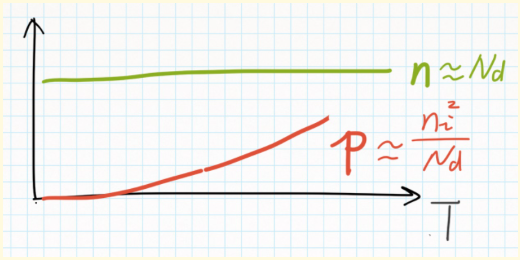

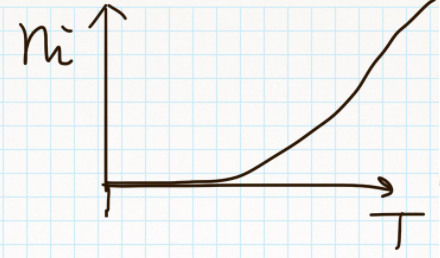

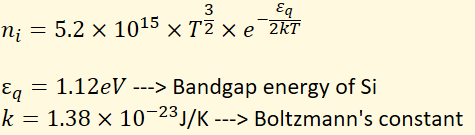

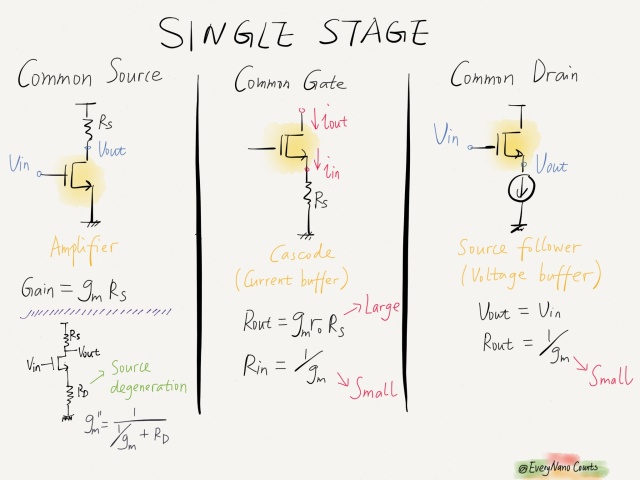

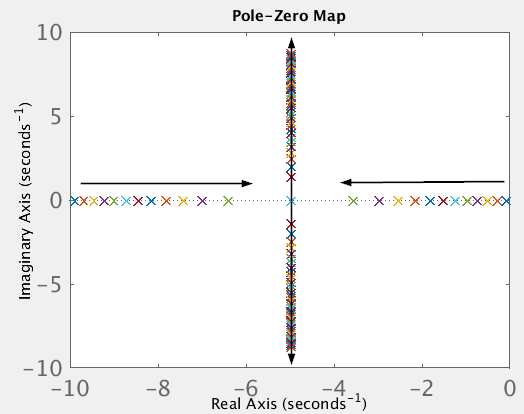

The good thing is that there are plenty of resources you can find from the internet; while the bad part is that after reading so much stuff it seems what I know about it is still these two curves… Frustrating!

In this post, the focus is not on the technical details of ADC design, but on sharing my experience of getting started with it. Mainly I will point out the good references which speed up my learning curve and prevent drowning in the

ADC sea of knowledge.

First, textbooks.

The popular yellow and green bibles are too difficult to digest for a newbie (BUT bibles are bibles! You will still need them time after time…). Until I found the data converter book written by Prof. Franco Maloberti, I just can’t stop reading its chapter 6 on oversampling and low order modulators. Besides a good explanatory flow, it also provides Matlab/Simulink models to vividly show the working algorithms and circuit defects of low order

ADC.

Second, lecture notes.

Prof. Gabor C. Temes’s course on oversampled Delta-Sigma data converters from OSU (accessed 06/02/2022).

Prof. Richard Scherier’s course on Advanced Analog Circuits from University of Toronto (accessed 06/02/2022).

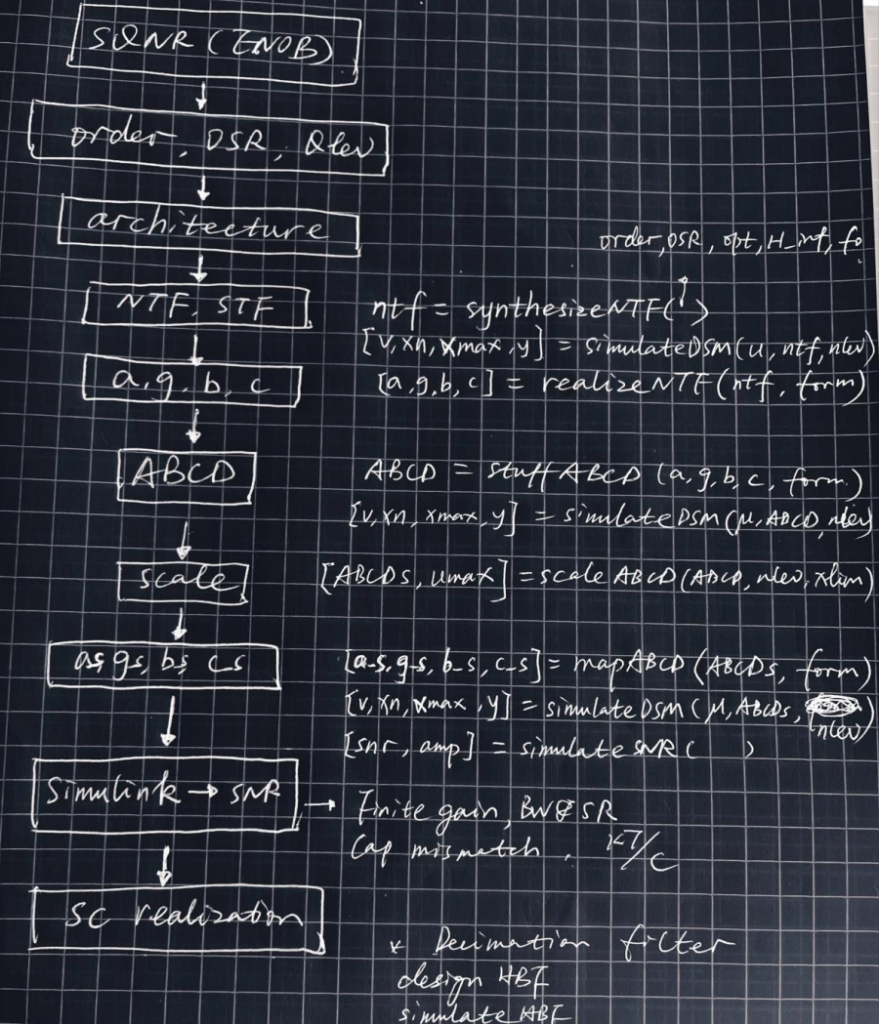

Prof. Vishal Saxena’s course on mixed-signal IC design (focused on Delta-Sigma ADCs) from Boise State University. I really like his hand-written lecture notes (accessed 06/02/2022).

Third, online resources.

cppsim.com by Michael H. Perrott. I benefit a lot from one of his tutorial (accessed 06/02/2022) on “Behavioral Simulation of A Second Order Discrete Time Delta‐Sigma ADC Using CppSim”. At the end of the document, there is an appendix on Matlab synthesis code based on Schreier’s Delta-Sigma Matlab Toolbox (very handy!).

Finally, I know … again … too much info here. Then stop reading, just start to create some behavioral model first!